由于數(shù)字電路抗干擾優(yōu)于模仿電路;電路結(jié)構(gòu)簡略;控制精度高且精確;同時易于開發(fā)和完結(jié);成本低價;運用方便等特色。所以數(shù)字電路在如今許多數(shù)字電路電子產(chǎn)品中,如家電、航空、交通、通信、醫(yī)療、自動化控制等領(lǐng)域廣泛運用。而在EUVIS數(shù)模轉(zhuǎn)化器中,常見的有DAC/ADC數(shù)模集成轉(zhuǎn)化器電路。

數(shù)字電路處理的信號是斷續(xù)改變的,可是大量受控終端執(zhí)行與反饋是模仿量連續(xù)改變的,如溫度、壓力、流量、速度等。以便于運算與控制,這就需要將數(shù)字信號轉(zhuǎn)化成模仿量;模仿量轉(zhuǎn)化成數(shù)字信號兩種相對應(yīng)的電路。即DAC/ ADC數(shù)模轉(zhuǎn)化器。

EUVIS 中DAC數(shù)模轉(zhuǎn)化器作用是,將數(shù)字電路的輸出的數(shù)字信號轉(zhuǎn)化成模仿信號的一種集成電路。

它有基準(zhǔn)電源、數(shù)字寄存器、模仿電子開關(guān)、權(quán)電阻網(wǎng)絡(luò)、求和運算放大器,以及抗干擾、防溫度漂移、增益和失調(diào)補償?shù)冉M成。

DAC數(shù)模轉(zhuǎn)化器分辯率:電路所能分辯的最小輸出電壓增量與滿刻度輸出電壓之比。即分辯率=1 /(2?-1)

因此DAC輸入位越多→分辯率越高→最小輸出電壓增量越小。

DAC數(shù)模轉(zhuǎn)化器精度:DAC數(shù)模轉(zhuǎn)化器實際輸出電壓與理論值之間的差錯。

影響的要素有:內(nèi)部電子元器件的參數(shù)的精確度、穩(wěn)定性、工作環(huán)境(如溫度,諧波、磁場)等

追求高分辯率,即輸入位越多,理論上可行,但實際情況是,當(dāng)內(nèi)部電子元器件數(shù)量增多,相同的電子元器件的參數(shù)等同度、精度就要求越高。這是較難辦到的。一般采取分辯率與精度彼此協(xié)調(diào)。一般精度差錯應(yīng)≤?最小輸出電壓增量。

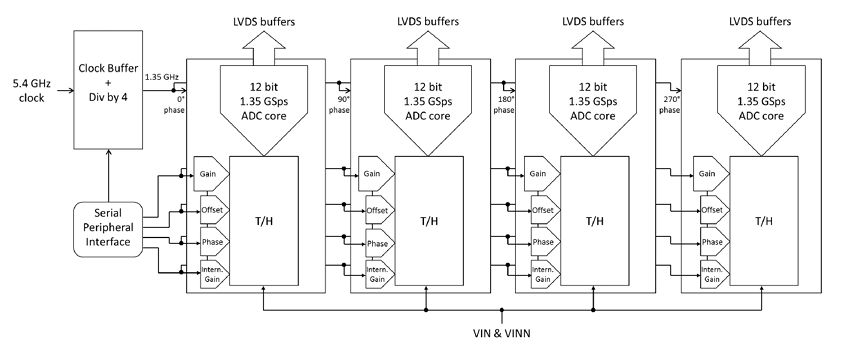

EUVIS 中ADC模數(shù)轉(zhuǎn)化器作用是,將來自外部受控終端的模仿量轉(zhuǎn)化成數(shù)字信號的一種集成電路。

ADC有采樣電路、保持電路、量化和編碼電路等組成,其中量化和編碼電路是ADC模數(shù)轉(zhuǎn)化器核心部分。

采樣電路是在周期的采樣脈沖控制下,完結(jié)來自外部受控終端的模仿量的采樣幅值。而保持電路是將采樣幅值保持到下一個采樣脈沖到來之前。在這段時刻內(nèi),采樣到的幅值經(jīng)量化和編碼電路后,輸出n位二進(jìn)制數(shù)字量。

要使ADC輸出n位二進(jìn)制數(shù)字量接近于模仿量,即失真度小。采樣周期及量化和編碼電路處理時刻長短;量化時差錯;以及電子元器件的參數(shù)的精確度、穩(wěn)定性、工作環(huán)境是關(guān)鍵。

量化和編碼電路有多種形式,如并行比較型;逐次比較型;雙積分型;計數(shù)型。

并行比較型特色:轉(zhuǎn)化速度快,但比較器數(shù)量多,關(guān)于n位數(shù)字量輸出需2?-1個比較器,適用于n≤4。

逐次比較型特色:電路簡略只有一個比較器,速度次于并行比較型,精度較高。適用于多位。

雙積分型特色:因選用雙積分轉(zhuǎn)化,所以速度較慢,轉(zhuǎn)化結(jié)果、精度不受積分器的R、C改變而影響。適用于工業(yè)外表。

計數(shù)型特色:電路簡略,輸出的數(shù)字量一直跟蹤輸入模仿量的改變。轉(zhuǎn)化速度最慢(n位需2?-1時鐘周期),為加快速度,采取添加一個可逆計數(shù)。

跟著電子器件結(jié)構(gòu)性的改變,量化和編碼電路較慢類型將會得到顯著的改進(jìn)。

深圳市立維創(chuàng)展科技是EUVIS數(shù)模轉(zhuǎn)換器的代理經(jīng)銷商,主要提供EUVIS的DAC、DDS、DAC等產(chǎn)品,原裝現(xiàn)貨,價格優(yōu)勢,歡迎咨詢

詳情了解EUVIS數(shù)模轉(zhuǎn)換器請點擊:http://www.bgbga.com/brand/24.html

更多產(chǎn)品咨詢,請聯(lián)系我們的銷售代表:0755-83050846 QQ: 3312069749